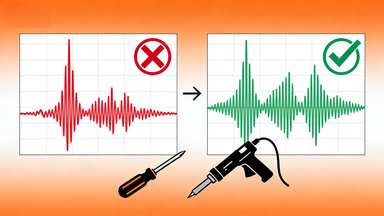

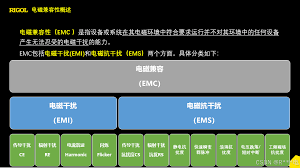

很多企业都有一个误区:EMC(电磁兼容)是测试出来的。其实不然,EMC是设计出来的。如果等到模具开了、PCB板定型了才去测EMC,一旦不合格,整改的代价将是巨大的(可能涉及割铜皮、飞线甚至报废模具)。因此,在产品开发的画图阶段就融入EMC思维,是降本增效的关键。

核心原则:源头抑制 > 路径切断 > 屏蔽

在设计初期,我们应遵循“预防为主”的策略,主要关注以下三个层面:

1. PCB层叠设计 (Layer Stackup)

这是最根本的EMC设计。

- 地平面完整性: 确保高频信号线下方有完整的地平面(Ground Plane)作为回流路径。永远不要让高速信号跨越地平面的分割缝隙。

- 电源层紧耦合: 电源层和地层应尽量靠近,形成天然的板间电容,滤除高频噪声。

2. 接口滤波设计 (Interface Filtering)

所有的对外接口(USB, LAN, Power)都是潜在的噪声出入口。

- 位置: 滤波器件(如共模电感、磁珠、电容)必须紧靠接口连接器放置。

- 隔离: I/O区域的地应当与数字逻辑地通过隔离岛或桥接方式处理,防止板内噪声耦合到线缆上。

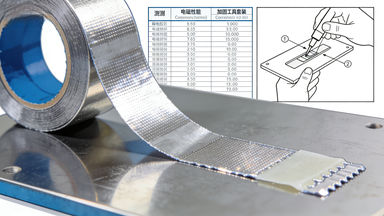

3. 结构屏蔽 (Shielding)

对于辐射特别强的器件(如DDR内存、主控CPU),预留屏蔽罩(Shielding Can)的位置。金属外壳产品要保证上下盖接触良好,形成法拉第笼。如果是塑料外壳,考虑是否需要喷导电漆。

研发阶段的检查清单 (Checklist)

- 晶振下方是否挖空了所有层?(防止耦合)

- 复位电路是否远离了干扰源?(防止误触发)

- 关键信号线(时钟、复位)是否包地处理?

- 连接器的金属外壳是否已良好接地?

总结

好的EMC设计是“隐形”的,它融入在走线的每一个拐角、每一个过孔之中。在开发阶段多花10%的时间考虑EMC,往往能在后期节省50%的整改时间和认证费用。

深圳晟安电磁提供产品设计阶段的EMC咨询服务。我们可以在您画原理图和Layout时介入,进行设计评审(Design Review),提前规避常见的EMC风险点,让您的产品“出生”即合规。